(la videolezione) Un display a 7 segmenti è un dispositivo elettronico per la visualizzazione di numeri, comunemente usata in orologi digitali, calcolatrici, e contatori. Il suo nome deriva dal fatto che è composto da sette segmenti luminosi (tipicamente LED), disposti a formare la cifra 8. Ogni segmento è un diodo a emissione luminosa (LED) che può essere acceso o spento individualmente. Combinando l'accensione e lo spegnimento dei vari segmenti, è possibile visualizzare tutte le cifre da 0 a 9.

I sette segmenti sono etichettati con le lettere da 'a' a 'g'.

Per visualizzare una cifra, si accendono solo i segmenti necessari. Ad esempio, per mostrare la cifra '1', si accendono solo i segmenti 'b' e 'c'. Per visualizzare lo '0', si accendono tutti i segmenti tranne il 'g'.

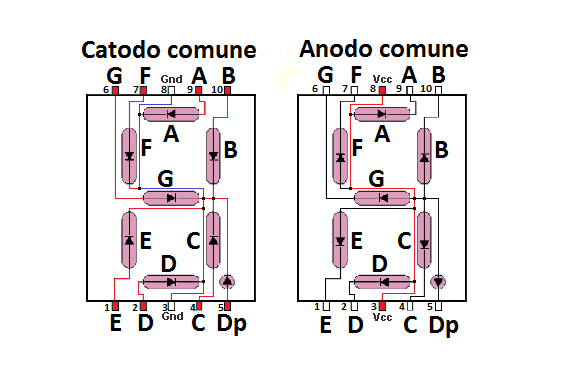

Esistono due configurazioni principali per i display a 7 segmenti:

Anodo Comune: Tutti i segmenti LED hanno i loro anodi (terminali positivi) collegati insieme a un'unica fonte di alimentazione positiva. Per accendere un segmento, si deve applicare una massa (0V) al suo rispettivo catodo (terminale negativo).

Catodo Comune: Tutti i catodi (terminali negativi) dei segmenti sono collegati insieme a un potenziale di terra. Per accendere un segmento, si deve applicare una tensione positiva (come +5V) al suo rispettivo anodo.

I vantaggi e gli svantaggi dell'uso di questo tipo di display possono essere così riassunti:

Semplice e affidabile: La sua struttura semplice lo rende facile da usare e molto robusto.

Economico: La tecnologia LED è molto economica, rendendo i display a 7 segmenti una soluzione a basso costo.

Luminosità: I LED offrono una buona luminosità e contrasto, rendendo i numeri facilmente leggibili.

Limitato: Può visualizzare solo numeri e un numero limitato di lettere.

Consumo energetico: Sebbene i singoli LED consumino poco, l'accensione di molti segmenti contemporaneamente può aumentare il consumo energetico.

.png)