Il funzionamento di base di un transistor MOSFET , cuore dell'elettronica digitale, è elegante nella sua semplicità. Due aree fortemente drogate (source e drain) sono separate da un substrato e un terminale di controllo (gate), isolato da uno strato di ossido, è affacciato sul canale tra di esse. Applicando una tensione al gate, si crea un campo elettrico che forma un canale conduttivo tra source e drain, controllando così il flusso di corrente.

Questa struttura, sviluppata principalmente in lunghezza e larghezza (da qui il nome "MOSFET planare"), ha guidato l'industria per anni. Ma spingendo la miniaturizzazione a lunghezze di canale inferiori a poche decine di nanometri, la fisica classica ha iniziato a vacillare. Due fenomeni critici sono emersi:

Dispersione di gate: la sottigliezza dello strato di ossido isolante ha portato a correnti di dispersione tra gate e substrato, aumentando consumi e generazione di calore.

Perdita di Controllo Electrostatico: drain e source diventano così vicini che la differenza di potenziale tra di loro è di per sé sufficiente a creare un percorso conduttivo, vanificando l'effetto di controllo del gate. Il transistor, in pratica, conduce corrente anche quando dovrebbe essere spento, smettendo di comportarsi come un interruttore.

Accorgimenti come la tecnologia SOI (Silicon On Insulator) hanno temporaneamente tamponato il problema della dispersione, ma non hanno risolto il cuore della questione: la struttura planare stessa, ridotta all'estremo, non era più in grado di controllare efficacemente il canale.

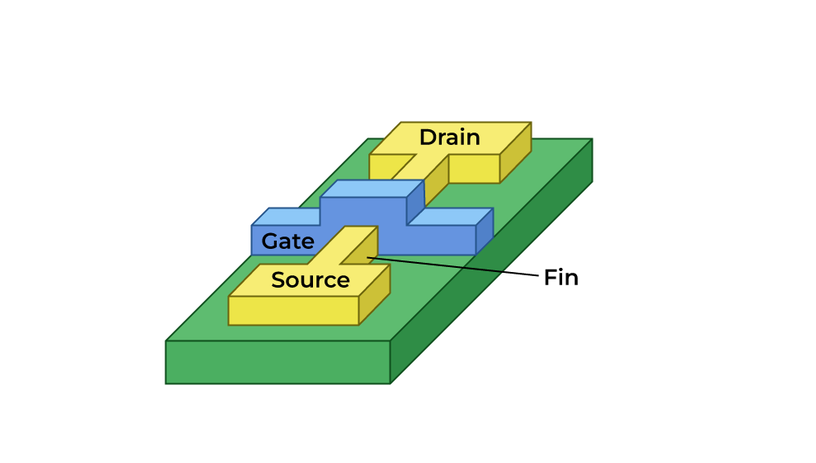

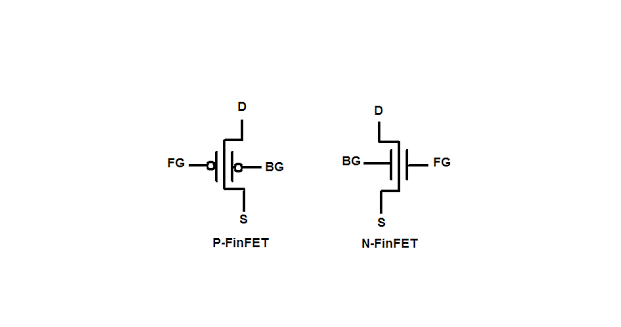

La risposta a questa crisi è arrivata da una rivoluzione concettuale: abbandonare il piano e aggiungere una dimensione. Un gruppo di ricerca dell'’Università di Berkeley in California ha proposto una struttura radicalmente nuova: il FinFET.

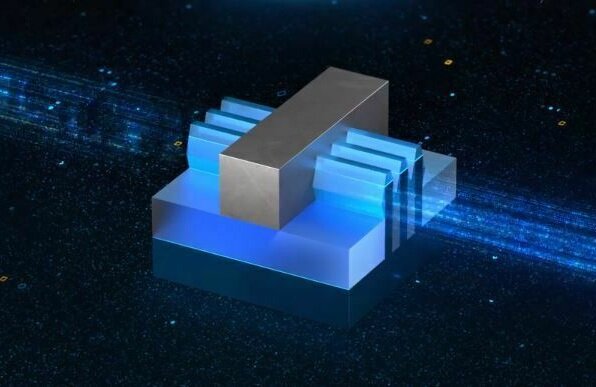

In questo transistor, il gate non è più semplicemente affacciato sul canale, ma lo avvolge completamente su tre lati, come un morso che stringe una pinna (in inglese, "fin") di silicio.

Questa architettura massimizza l'accoppiamento elettrostatico tra gate e canale, ripristinando un controllo efficace anche a lunghezze infinitesime. Inoltre, viene eliminato il silicio in eccesso sotto il canale, fonte di dispersione aggiuntiva. La corrente fluisce parallelamente alla superficie del wafer all'interno della "pinna", e la struttura attiva si sviluppa in altezza, dando vita a una vera e propria elettronica 3D.

I vantaggi sono sostanziali: un FinFET è stimato essere fino al 30% più veloce e molto più efficiente dal punto di vista energetico di un omologo planare a parità di dimensioni. Ciò permette di ridurre la tensione di alimentazione, dissipare meno calore e integrare un numero maggiore di transistor a parità di superficie.

Tuttavia, il passaggio al FinFET non è stato immediato. Sono passati oltre dieci anni dalla proposta alla produzione in serie a causa di sfide immense:

Progettazione: è stato necessario sviluppare un ecosistema CAD completamente nuovo per gestire la complessità geometrica e modellare parametri parassiti ben più intricati.

Produzione: richiede un costoso adeguamento delle linee di produzione ed è molto sensibile alle naturali variazioni di processo, come la larghezza della pinna di silicio.

Costo: il passaggio a una tecnologia FINFET da una planare comporta un aumento dei costi del 50%.

Proprio il fattore costo e la complessità hanno aperto la strada a un valido concorrente, specialmente in certi segmenti di mercato: la tecnologia FD-SOI (Fully Depleted - Silicon On Insulator). Questa evoluzione della struttura planare utilizza wafer con uno strato isolante che permette un buon controllo del canale, minore dispersione e la possibilità di utilizzare tecniche per bilanciare consumi e prestazioni. Essendo basata su un processo planare maturo, FD-SOI offre minori rischi produttivi, costi inferiori e una più semplice integrazione di componenti analogici ed RF, riutilizzando progetti collaudati.

Il futuro dell'industria dei semiconduttori si prospetta quindi vivace e diversificato: i FINFET domineranno l’high-performance computing e le applicazioni dove massima velocità e miniaturizzazione spinta sono essenziali. Le tecnologie FD-SOI e simili troveranno ampio spazio in settori come IoT, automotive ed elettronica embedded, dove costo, bassissimo consumo e facilità di integrazione sono più importanti delle grandi prestazioni.

Sebbene invisibili all'utente finale, i FINFET sono già tra noi dal 2015. Samsung li ha utilizzati un suo processore per smartphone, abilitando core ad alte prestazioni e a basso consumo per un bilanciamento ottimale tra potenza di calcolo e autonomia. AMD li ha adottati per le sue schede alcune grafiche, dove l’efficienza del FINFET, unita a tecniche avanzate ha permesso di raggiungere capacità di calcolo nell'ordine dei TeraFLOPs con consumi contenuti.

.png)